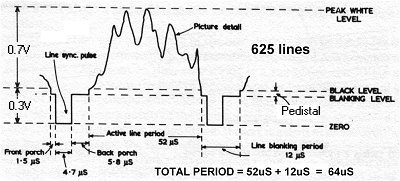

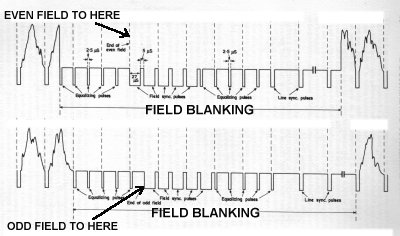

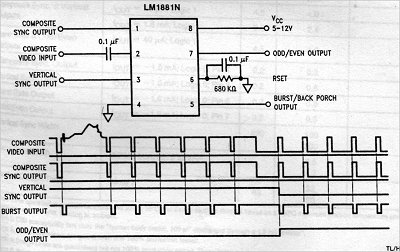

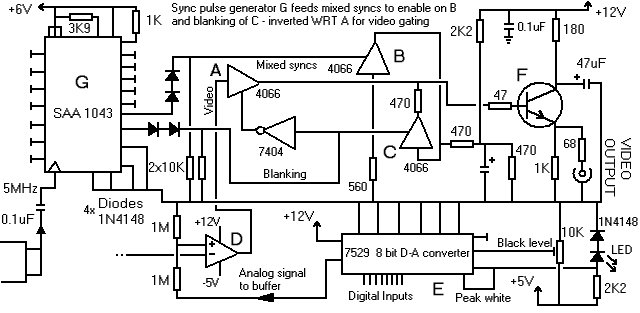

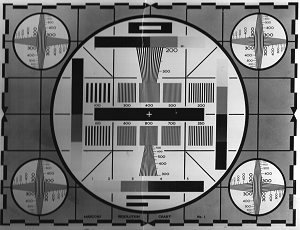

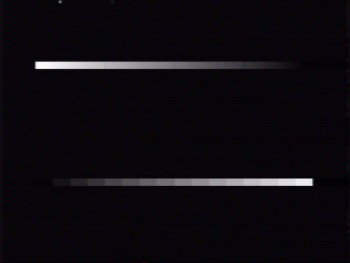

A video signal consists of a reference signal level we shall call ‘ground’, with synchronising pulses 0.3Volts below this level and a varying picture information signal up to a maximum of 0.6Volts above this level. (These voltages assume a correctly terminated signal - usually 75 ohms.) Obviously all of these events have to appear at the right time in order to be successfully ‘matched’ to a composite monitor (display). Now there are many ways of creating all those pulses in the right order, but in order to make things a little easier for oneself (especially if one has the job of creating a digital picture interface) I would strongly recommend using an SPG chip to do this part. SPG? Sync pulse generator. This IC, when given a suitable clock input, and genlock phase locked loop (PLL) if desired, will give the correct sequence of pulses for the TV standard required. It will still be necessary to make a proper interface however, to mate the SPG to the actual monitor itself. As far as the digital interface is concerned, it will be necessary to investigate the chosen SPG chip to see what output signals are available for the micro (hopefully at TTL level) By using these signals, it will then be possible to work out the times during the video signal itself when one can download information into the Video RAM being used for the display without interfering with the actual picture whilst it’s being displayed. The circuitry examples given here are extremely simple, but have been tried and tested and worked extremely well in the receiver of my Video Transmission Unit. Of course, the resolution is pretty poor - as to be expected with the amount of RAM being used (about 11K for the whole picture) - but there is nothing to stop anyone adding more RAM and using a much faster processor to achieve a far more detailed picture. As you can see, the actual ‘video generating’ bit of circuitry is totally free-running and does not need to use the processor to give a picture. As soon as the processor comes ‘on-line’ so to speak, IT has to synchronise it’s data transfer to coincide with blank portions of the display. |